**GENERAL**

**CORPORATION**

### General Robotics Corporation

### RXV21 USER MANUAL

740-1028-E0

### Revision Table

| DATE   | DESCRIPTION                                         |

|--------|-----------------------------------------------------|

| MAY 82 |                                                     |

| AUG 83 | Manual Edit                                         |

| OCT 83 | Manual Corrections                                  |

| MAR 84 | Manual Reformat; Table 2.4-D, re: Qume Drive, Added |

| NOV 84 | Revised and Corrected.                              |

| JAN 85 | Additions and Corrections                           |

NOTE: Date indicates current level of manual revision.

General Robotics Corporation 57 North Main Street Hartford, WI 53027

Toll Free - 800-742-5264 All Others- 414-673-6800

### TABLE OF CONTENTS

| 1.  | General Information                                            | 1        |

|-----|----------------------------------------------------------------|----------|

|     | 1.1 Introduction                                               | 1        |

|     | 1.2 Components                                                 | 2        |

|     | 1.3 Compatibility                                              | 2        |

|     | 1.3.1 Logical Track Format                                     | 2        |

|     |                                                                | 4        |

|     | 1.3.2 Sector Header Field                                      | 4        |

|     | 1.3.3 Data Field                                               | 5        |

|     | 1.3.4 Recording Scheme                                         | 5        |

|     | 1.3.5 Double Frequency (FM)                                    |          |

|     | 1.3.6 DEC Modified MFM                                         | 6        |

|     | 1.3.7 Cyclic Redundancy Check                                  | 7        |

|     | 1.4 Specification                                              | 7        |

| 2.  |                                                                | 8        |

| ~ • | 110001101011011011011011011011011011011                        |          |

|     | 2.1 Configuration                                              | 8        |

|     | 2.1.1 Address Vector Selection                                 | 11       |

|     | Z.1.1 Address vector selection                                 | 11       |

|     | 2.1.2 Device Interrupt Priority                                |          |

|     | 2.1.3 Bootstrap                                                | 11       |

|     | 2.1.4 Write Precompensation                                    | 12       |

|     | 2.1.5 Write Current Control                                    | 12       |

|     | 2.1.6 Drive and Side Selection                                 | 12       |

|     | 2.2 Drive Configuration                                        | 13       |

|     | 2.3 Cabling                                                    | 18       |

|     |                                                                | 10       |

|     | 2.5 Initial Operation and Checkout                             | 20       |

| 2   |                                                                | 22       |

| 3.  | Functional Description                                         | 22       |

|     |                                                                | 2.2      |

|     | 3.1 General                                                    | 22       |

|     | 3.2 Register Definitions                                       | 22       |

|     | 3.2.2 RXVDB Data Buffer                                        | 24       |

|     | 3.2.3 Extended Status Registers                                | 29       |

|     | 3.3 Command Protocol                                           | 31       |

|     | 3.3.1 Fill Buffer                                              | 31       |

|     | 3.3.2 Empty Buffer                                             | 32       |

|     | 3.3.3 Write Sector                                             | 32       |

|     | 3.3.4 Read Sector                                              | 33       |

|     | 3.3.5 Set Media Density                                        | 34       |

|     | 3.3.6 Read Status                                              | 35       |

|     |                                                                | 35       |

|     |                                                                | 3.<br>36 |

|     | 3.3.8 Read Error Code                                          |          |

| 4.  | . Controller Operations                                        | 37       |

|     |                                                                |          |

|     | 4.1 General                                                    | 37       |

|     | 4.2 Bootstrapping the Controller                               | 37       |

|     | 4.1.1 Bootstrap Operation                                      | 37       |

|     | 4.3 Format Operations                                          | 38       |

|     | 4.4 Fill/Write Operations                                      | 40       |

|     | 4.5 Read/Empty Operations                                      | 4        |

|     | 4.6 Write Current Control                                      | 42       |

|     | 440 HITE OUTLETT CONCIOT 6 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 | 7 (      |

## RXV21 User's Manual

| 4.7  | Write  | Precompensation                          | /. 3 |

|------|--------|------------------------------------------|------|

| /ı Q | Dorras | e Foil Deservat                          | 4.)  |

| 4.0  | rowei  | r Fail Protection                        | 43   |

| 4.9  | Opera  | ation and Format Using RT11              | 1.1  |

|      | A 1    |                                          | 44   |

| 4.   | 9.1    | Copying a DY Compatible Release Diskette | 44   |

| 4.   | 9.2    | Installing DY under RSX                  | , -  |

| • •  |        | installing by under RSA                  | 45   |

### GENERAL INFORMATION

The purpose of this manual is to provide the user adequate information to configure and operate the RXV21 floppy disk controller. The information provided should clarify the controller connection to any Shugart compatible drive and assist in the selection of associated interface options. Both register definition and command protocol are provided for reference and as an aid in development of user software. Operational procedures outline the use of the controller features as well as explaining operation in an RT11\* software environment.

#### 1.1 Introduction

The RXV21 is a dual density controller compatible with the DEC\* RXO2\* floppy disk system. Configured with any Shugart compatible drive, it is a direct replacement for the DEC RXV21 subsystem. The controller provides either single density encoding compatible with IBM 3740 equipment or double density encoding, providing 512K bytes of storage on a single diskette. When configured with two drives, each drive may operate at a different density.

All electronics are contained on one dual height module which plugs directly into any standard LSI-11\* backplane and interfaces through a 50 conductor ribbon cable to any Shugart compatible drive. All controllers are 100% tested and ready for operation. The controller is configured for the standard device address 777170 (octal) and interrupt vector 264 (octal). The interrupt level is factory set to level four. Features include:

- Transparent firmware bootstrap automatically loads either single or Double density diskettes. double density diskettes.

- Formatting capability permits writing sector headers, checking the written headers, and writing the data fields in the user selected density.

- Jumpers allow user selection of both the alternate address and vector.

- Jumper selectable four-level device interrupt priority compatible with the LSI-11/23.

- Provides power fail protection for data integrity.

- Write current control signal for tracks greater than forty-three.

- Write precompensation for reduced error rates.

- Bus Loads: AC-3; DC-1

- \*TM of Digital Equipment Corporation

### 1.2 Components

The controller is provided with the following components:

RXV21 Floppy Disk Controller Module RXV21 User's Manual

### 1.3 Compatibility

This section discusses the aspects of hardware, software and media compatibility with Digital Equipment's RX02 system. The information will aid the user in data interchange with foreign systems.

## Hardware Compatibility

The controller is compatible with the LST-11, LST-11/2 and LST-11/23 family of processors. All circuity is contained on one dual height module that plugs directly into any standard LST-11 backplane. Alternate address selection and a four level device interrupt priority scheme provide the user added flexibility for expanded system configurations. Shugart compatible drive logic is interfaced through a 50 pin ribbon connector. The interface is compatible with both the Shugart model 800 and 850 series drives.

## Software Compatibility

The RXV21 is completely compatible with RXV21 register definitions and command protocol. All DEC-supplied software designed to operate with the RX02 system will operate with the controller without modification. However, for RX03 usage the DEC supplied handler for RT11 (DY) has an error which does not allow automatic sensing of double side ready. The handler supplied by GRC has been corrected for this function.

## Media Compatibility

The media used with the RXV21 is compatible with the IBM 3740 family of equipment. Either preformatted or blank soft sectored diskettes may be used with the controller.

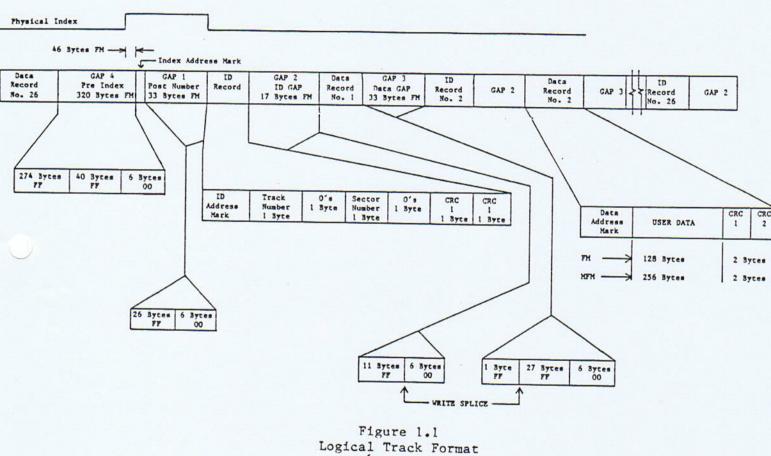

## 1.3.1 Logical Track Format

The diskette surface is divided into 77 concentric tracks numbered 0 - 76. Each track consists of 26 sectors numbered 1 - 26. The track begins and ends at the index address mark. The track is formatted in such a way that this soft index is preceded by the leading edge of the physical index hole in the diskette. Following the physical index are 40 bytes of 'FF' data, 6 bytes of '0' data, and the index address mark indicating the beginning of the track. Following the index address mark is the post index gap consisting of 26 bytes of 'FF' data and 6 bytes of '0' data. The next field is the sector header for sector 1. Following the sector header is the ID gap consisting of 11 bytes of 'FF' data and 6 bytes of

RX-03

GRC handler for RX-03 '0' data. The next field is the data record for sector 1. Following the data field is the data gap consisting of 28 bytes of 'FF' data and 6 bytes of '0' data. This field leads to the next sector header. Following the 26th data record is the pre-index gap consisting of approximately 274 bytes of 'FF' data.

Each track is formatted in the above manner. Refer to Figure 1.1. The sector header field of each sector contains information describing both the sector and track number. All the above fields are recorded in FM except as noted in the following sections.

3

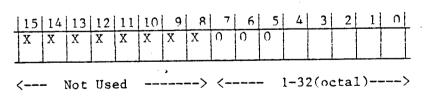

#### 1.3.2 Sector Header Field

The header field consists of 7 bytes of information. Preceding the header is a field of 6 bytes of '0' data for synchronization. The header and this preamble are always recorded in FM.

- Byte 1, ID Address Mark A unique mark consisting of 1 byte of FE (hex) data with three missing clock transitions using a C7 (hex) clock pattern. This mark is decoded by the controller and indicates the start of the sector header.

- 2. Byte 2, Track Address This byte indicates the absolute (0 114 octal) track address. Each sector contains this track information to locate its position on one of the 77 tracks.

- 3. Byte 3, Zero

- 4. Byte 4, Sector Address This byte indicates the absolute (1-32 octal) sector address. Each sector contains this information to identify its position on the track.

- 5. Byte 5, Zero

- 6. Bytes 6 and 7, CRC This is the 16 bit cyclic redundancy character and is calculated for each header from the first 5 bytes of information, using the IBM 3740 polynomial. Refer to Cyclic Redundancy Check, Section 1.3.7.

#### 1.3.3 Data Field

The data field consists of either 131 (decimal) or 259 (decimal) bytes of information depending upon the recording method. Preceding the data field is a field of 6 bytes of '0' data for synchronization.

The preamble and data address mark are always written in FM. The user data and CRC character are either written in FM or modified MFM depending upon the formatted diskette density.

Byte 1, Data Address Mark - A unique mark consisting of a data byte (see Table 1.1) with three missing clock transitions using a C7 (hex) clock pattern. This byte is always written in FM and is decoded by the controller to indicate the start of the data field, its recording method (FM vs. MFM), and if the field is a deleted data field.

| ADDRESS<br>MARK | INDICATED DENSITY | DATTA | CT OCT |

|-----------------|-------------------|-------|--------|

| MARK            | DENSIII           | DATA  | CLOCK  |

| INDEX           | N/A               | FC    | C7     |

| ID              | N/A               | FE    | C7     |

| DATA            | FM                | FB    | C7     |

|                 | MFM<br>Modified   | FD    | C7     |

| DELETED         | FM                | F8    | C7     |

| DATA            | MFM<br>Modified   | Fo    | C7     |

Table 1.1 Address Marks

- 2. Bytes 2 through 129 (FM) or bytes 2 through 257 (MFM modified) User data. This field is recorded in either FM or MFM modified. Depending upon the encoding scheme, either 128 or 256 bytes of information can be stored.

- 3. Bytes 130 through 131 or bytes 258 through 259, CRC This is the 16 bit cyclic redundancy character and is calculated for each data field from the first 129 or 257 bytes of information using the IBM 3740 polynomial. Refer to Cyclic Redundancy Check, Section 1.3.7. These bytes are recorded with the same encoding scheme as the data field.

### 1.3.4 Recording Scheme

Two recording schemes are used by the RXV21: Double frequency (FM) and DEC modified Miller code (MFM). FM is used for single density recording and is compatible with IBM 3740 or DEC RX01 media. DEC modified MFM is used for recording double dénsity and is only compatible with the DEC RX02 system.

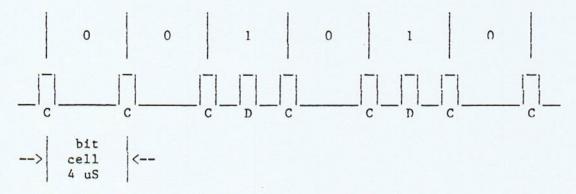

### 1.3.5 Double Frequency (FM)

FM recording is charactierized by a flux transition at the beginning of each bit cell which is commonly termed a clock pulse or transition as shown in Figure 1.2. A logic 'l' is represented by a flux transition within the bit cell; a logic 'O' is represented by the lack of any flux transition within a bit cell. In FM the bit cell time is 4 microseconds.

Figure 1.2 FM Recording Charactistics

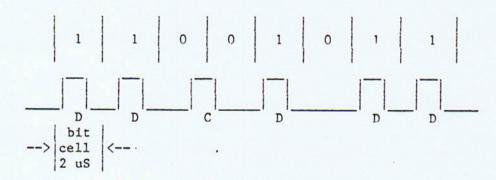

### 1.3.6 DEC Modified MFM

MFM recording consists of flux transitions for a logic 'l' and no flux transitions for a logic '0'. A clock transistion only occurs between two consecutive logic '0' states as shown in Figure 1.3 below. The MFM bit cell time is 2 microseconds.

Figure 1.3

MFM Recording Characteristics

Table 1.2 summarizes the standard MFM encoding algorithm.

| DAT  | A  | ENC  | ODED DA | ATA |

|------|----|------|---------|-----|

| DN-1 | DN | DN-1 | CN      | DN  |

| 0    | 0  | 0    | 1       | 0   |

| 1    | 0  | 1    | 0       | 0   |

| 0    | 1  | 0    | 0       | 1   |

| 1    | 1  | 1    | 0       | 1   |

Table 1.2 Standard MFM Encoding

Because single density headers are used for both FM and MFM recording formats, and since certain MFM patterns map into single density address marks, a modified algorithm is used. The mapping occurs when a data pattern of exactly four consecutive 'l' states is encoded. Whenever this pattern is encoded a special algorithm is applied. Table 1.3 defines the encoding algorithm for this special case.

| Dn-1             | Do        |

|------------------|-----------|

| 1                | Dn<br>O   |

| 0 0<br>Cn-1 Dn-1 | l 1 0     |

| _                | Cn-1 Dn-1 |

Table 1.3 Modifying Algorithm (Special Case)

When reading double density data fields the controller checks for a missing clock bit between two zero data cells, and if found, substitutes ones for the two zero data bits (generated by the special encoding algorithm).

### 1.3.7 Cyclic Redundancy Check

Each sector header field and data field has a two byte CRC character appended. This 16 bit character is the remainder that results when dividing the data bits [represented as a polynomial M(x)] by a generator polynomial G(x). The polynomial use for IBM 3740 is G(x)=x16+x12+x5+1. For the sector header the data bits include byte 1 through byte 5. For an FM data field the data bits include byte 1 through byte 129. For an MFM data field the data bits include byte 1 through byte 257.

#### 1.4 Specification

#### RECORDING TECHNIQUE:

Single Density IBM 3740 FM

Double Density DEC Modified MFM

#### POWER REQUIREMENTS:

Voltage 5 VDC (from LSI-11 backplane) Current 2.5 A typical

#### ENVIRONMENTAL:

Temperature 0-45 degrees C Humidity 10-95 % non-condensing

### 2. INSTALLATION

### 2.1 Configuration

The controller is shipped with standard options configured. The standard address 777170 (octal) and vector 264 (octal) are set. The device interrupt priority is set to level four. The firmware bootstrap is disabled. Write precompensation is enabled. Write current control is disabled. Both drive and side select options have been configured for either single or double sided drives.

Most options are factory foil-etched to the most often used configuration. The foil jumpers must first be cut before the alternate jumpers are inserted. Refer to Tables 2.1, 2.2, and 2.3 for alternate options and Figure 2.1 for jumper location. Several of the options are selectable by using AMP 530153-2 pin jumpers. If these pin jumpers are not available use #30 AWG wire wrap wire.

| OPTION                                    | JUMPERS |       |       |  |  |  |

|-------------------------------------------|---------|-------|-------|--|--|--|

|                                           | 15-16   | 16-17 | 33-34 |  |  |  |

| Standard<br>Address/Vector*<br>777170/264 | In      | Out   | Out   |  |  |  |

| Alternate<br>Address/vector<br>777174/270 | Out     | In    | In    |  |  |  |

Table 2.1 Address/Vector Option Configuration

| Priority | Assert | Monitor | 70 |     |    |    | Jump | er |    |    |     |     |   |

|----------|--------|---------|----|-----|----|----|------|----|----|----|-----|-----|---|

|          | Level  |         | 18 | 119 | 21 | 22 | 24   | 25 | 27 | 28 | 130 | 131 |   |

|          |        |         | to | to  | to | to | to   | to | to | to | to  | to  |   |

|          |        |         | 19 | 20  | 22 | 23 | 25   | 26 | 28 | 29 | 31  | 32  |   |

| 4 *      | 4      | 5,6     | 0  | I   | 0  | I  | T.   | 0  | 0  | T. | I   | 0   | V |

| 5        | 4,5    | 6       | 0  | I   | I  | 0  | I    | 0  | 0  | T. | 0   | T   |   |

| 6        | 4,6    | 7       | I  | 0   | 0  | I  | 0    | T  | T  | 0  | T   | 0   |   |

| 7        | 4,6,7  | none    | I  | 0   | I  | 0  | 0    | I. | I  | 0  | 0   | T   |   |

\* factory preset

I=IN

O=OUT

Table 2.2: Priority Level Configuration

| OPTION                      | JUMPERS FUNCTION  10-11 Enabled            |

|-----------------------------|--------------------------------------------|

| Bootstrap                   | 10-11 Enabled<br>10-43* Disabled           |

| Write Precomp               | 13-14* Enabled<br>13-12 Disabled           |

| Write Current               | 13-12 Disabled  8-9 Enabled & The Disabled |

| Single Sided<br>Drives Only | 2-3 IN<br>5-7 IN                           |

|                             | 1-2 OUT<br>4-5 OUT<br>5-6 OUT              |

| Single or<br>Double Sided   | 2-3* IN *=factory preset<br>4-5* IN        |

|                             | 1-2* OUT<br>5-6* OUT<br>5-7* OUT           |

Table 2.3 Miscellaneous Options Configurations

(unte cu RXV21 User's Manual WRITE CURRENT DRIVE SELECT @ 1983 GENERAL ROBOTICS CORP. SIDE SELECT ZI 21001 >1002 >1004 21000 21003 1005 2911 TEST GRC RXV21 P/N27-0028 21010 )LS374 \LS374 Z )LS374 13 2911 2911 )SI24 22 uf TEST 22 220 TEST ) | | 74123 2901 LS253 2901 74 92 LS251 R C18 821 ALT ADDR æ )s 2 74276 Z30 221 100 n C27 Z27 ALT VECTOR Z28 LS 25 I )12.0MI BOOTSTRAP PRECOMP 748-0028-E0 TEST GI4 GI3 GI2 Z40 Bootstrap 2006 SIO 232 7438 )LS175 )5139 LS251 LS164 1007 at a time in the C21 248 MADE IN USA CZZ System Z49 % ₹ \LS259 **Z52** \LS257 8641 \LS259 304 8641 53 005 INTERRUPT PRIORITY Z58 C14 C13 257 ZEOCIS 259 E)8641 Z84 C17 LS257 8641 502 8641 8640 TMS 4044 4 2 2 2 2 2 2 7438 8 64 INTERRUPT PRIORITY

Figure 2-1: Configuration Jumper locations REV. E

GII GIO G43

Board

Board

Lisablet

### 2.1.1 Address Vector Selection

The controller is shipped with the DEC standard device address and vector assignments preset to 777170 (octal) and 264 (octal), respectively. Any change in these assignments would necessitate a change in system software. However, and alternate address and vector assignment is selectable and is defined as 777174 (octal) and 270 (octal) respectively.

These assignments are typically used when more than two drives are needed; two controllers would be required and the second controller would be configured for the alternate address and vector. To select the alternate address and vector, first cut the foil between G15 and G16. Jumper G16 to G17 and jumper G33 to G34 as shown in Table 2.1.

### 2.1.2 Device Interrupt Priority

The RXV21 supports the four level device interrupt priority scheme compatible with the LSI-11/23. The controller asserts interrupt requests and monitors higher level request lines during interrupt arbitration as described in Table 2.2. The level four request is always asserted by the controller, regardless of its priority, to maintain compatiblilty with the LSI-11 and LSI-11/2 processors.

The interrupt priority level is configured to level four at the factory. If a different interrupt level is desired the following foil-etched jumpers must be cut. Refer to Table 2.2 for the proper jumpers to insert for the desired priority level.

G19 - G20 G22 - G23 G24 - G25 G28 - G29

G30 - G31

### 2.1.3 Bootstrap

The controller board incorporates a transparent firmware bootstrap. The bootstrap is initiated whenever program execution is started at location 773000 (octal), homing both drives to track 0. Next, track 1, sector 1 of unit 0 is read and the diskette density is determined. If the diskette is single density, sectors 1, 3, 5, and 7 are loaded into memory starting at location 0. If the diskette is double density, sectors 1 and 3 are loaded. Program execution is then transferred to location 0. Controllers are shipped with this feature disabled. To enable the bootstrap remove the jumper from G43-G10 and insert the jumper between G10 and G11 as shown in Table 2.3.

#### \*\*\*\*CAUTIONARY NOTE\*\*\*\*

Rev D boards had a layout error which swapped G10 and G11, G43 should never be connected to G11 on these or any other boards.

#### --- NOTE ---

Only one bootstrap should be enabled in a system for proper operation. If another bootstrap exists in the system, it must be disabled before enabling the controller bootstrap.

### 2.1.4 Write Precompensation

The RXV2l controller provides hardware write precompensation to reduce the bit shift exhibited by all drives as the recorded flux density increases. The controller recognizes the patterns which produce bit shift and precompensates the written pattern. This unique feature allows the controller to perform reliably with any Shugart Compatible drive.

Controllers are shipped with this feature enabled and it is recommended that for more reliable operation the feature not be disabled. However, if so desired, the feature can be defeated by cutting the foil-etched jumper between G13 and G14 and inserting a jumper between G12 and G13 as shown in Table 2.3.

#### 2.1.5 Write Current Control

The RXV21 provides the necessary signal to reduce the write current for tracks greater than forty-three. This signal is available at pin 2 of the 50 pin ribbon connector.

Since the Shugart model 800 series single sided drives do not require a write current signal, the controller is shipped with this feature disabled. However, the double sided 850 series drives do support write current control, and enabling this feature is recommended for reliable operation. This may be accomplished by jumpering pins G8 and G9 as shown in Table 2.3.

### 2.1.6 Drive and Side Selection

The controller features several options for both drive and side selection. The side select output can be disabled, allowing operation on single sided drives only. The controller can be configured for either single or double sided drives. Proper jumpering allows one double sided

drive to be addressed as two drives where side 0 appears as drive 1 and side 1 appears as drive 2. However in this mode the controller will give seek errors if a seek to a different track is done on drive A between two accesses on drive B, because the controller is expecting the two drives to have separate seek mechanisms and finds that it is not on the correct track.

The controller, when shipped, is configured for either single or double sided drives. If double sided drives are used, it is recommended that the write current control be enabled as described in Section 2.1.5. Before selecting alternate options the foil-etched jumper between G4 and G5 must be cut. For alternate configurations refer to Table 2.3.

#### 2.2 Drive Configuration

For proper operation, the floppy drives must be configured with attention to several options. The controller uses radial drive selection. Thus the drive(s) should be correspondingly configured. When two drives are used, the first should be drive I and the second drive 2. A particular drive is selected and remains selected after a function is complete to allow the controller to poll drive status. A separate head load signal is provided by the controller for read and write functions on the diskette. The 'IN USE' logic of the drive should be configured as a function of head loading. Since the drives are homed without loading the heads during an initialize command, the drive should be configured to provide stepper motor power independent of head loading. Refer to Table 2.4 for details concerning these and other options.

Gy of h

Margar 800

| •   |                              | DU           | AL      | STNGLE  |

|-----|------------------------------|--------------|---------|---------|

| OPT | DESCRIPTION                  | CRIS DRIVE O | DRIVE 1 | DRIVE O |

| DS1 | Drive Select 1               | out In       | Out     | In      |

| DS2 | Drive Select 2               | Out          | In      | Out     |

| DS3 | Drive Select 3               | (N) Out      | Out     | Out     |

| DS4 | Drive Select 4               | Out          | Out     | Out     |

| A   | Radial head loading option   | In           | Tn      | In      |

| В   | Radial head loading option   | √Tn          | T.n     | In      |

| C   | Head load option             | In           | In      | In      |

| D   | In use option                | Out          | Out     | Out     |

| X   | Radial head loading option   | IN Out       | Out     | Out     |

| WP  | Inhibit write when protect   | In           | In      | In      |

| NP  | Allow write when protect     | Out          | Out     | Out     |

| DS  | Stepper power from drive se  | lect In      | In      | In      |

| HL  | Stepper power from head load |              | Out     | Out     |

| Z   | In use from drive select     | / N Out      | Out     | Out     |

| Y   | In use from head load        | OUT In       | In      | In      |

| R   | Ready output                 | In           | In      | Tn      |

| I   | Index output                 | In           | In      | In      |

| DC  | Disk change output           | X            | X       | X       |

| S   | Sector output                | X            | X       | X       |

| 800 | Sector option Disable        | In           | Tn      | In      |

| 801 | Sector option Enable         | Out          | Out     | Out     |

| L   | -5V DC Bias                  | In           | In      | In      |

| Tl  | Termination HL               | *            | *       | In      |

| T2  | Termination Drive Select     | *            | *       | Tn      |

| T3  | Termination Direction        | *            | *       | In      |

| T4  | Termination Step             | *            | *       | In      |

| T5  | Termination Write Data       | *            | *       | In      |

| T6  | Termination Write Gate       | *            | . *     | In      |

<sup>\*</sup> Terminators should be placed 'IN' on the drive which is physically the last one on the cable.

Note: 800 Series drives may require 10 millisecond step rate PROMS to operate properly. This PROM is located in socket Z7. Factory standard PROM is 3 millisecond.

Table 2.4-A: Drive Configuration Shugart 800/801 Drives

# Schugas 850

|                             | DU      | AL      | SINGLE  |

|-----------------------------|---------|---------|---------|

| OPTION                      | DRIVE O | DRIVE 1 | DRIVE C |

| DS1                         | In      | Out     | In      |

| DS2                         | Out     | In      | Out     |

| DS3                         | Out     | Out     | Out     |

| DS4                         | Out     | Out     | Out     |

| Resistor)LOC H2<br>Network) | *       | *       | In      |

| 2S                          | In      | In      | In      |

| DC                          | X IN    | X       | X       |

| D                           | Out     | Out     | Out     |

| S1                          | Out     | Out     | Out     |

| S2                          | In      | In      | In      |

| S3                          | Out     | Out     | Out     |

| H1                          | In      | In      | In      |

| C                           | In      | In      | In      |

| IT                          | Out     | Out     | Out     |

| Z                           | Out     | Out     | Out     |

| HL                          | Out     | Out     | Out     |

| A                           | In      | In      | Tn      |

| В                           | Out     | Out     | Out     |

| X                           | In      | In      | In      |

| I                           | In      | In      | Tn      |

| R                           | In      | In      | In      |

| S                           | X       | X       | X       |

| DS                          | In      | In      | In      |

| HLL                         | Out     | Out     | Out     |

| DL                          | Out     | Out     | Out     |

| Y                           | In      | In      | In      |

| IW                          | Out     | Out     | Out     |

| RS .                        | Out     | Out     | Out     |

| RM                          | In      | In      | In      |

| 851                         | Out     | Out     | Out     |

| 850                         | In      | In      | In      |

| TS                          | X       | X       | X       |

| FS                          | X       | X       | Х       |

<sup>\*</sup> Terminators should be placed 'IN' on the drive which is  $\mbox{phy-sically}$  the last one on the cable.

Table 2.4-B: Drive Configuration Shugart 850/851 Drives Configured for RXO3 Compatibility COC

|        |         | DUAL | SINGLE  |

|--------|---------|------|---------|

| OPTION | DRIVE O |      | DRIVE O |

| DS1    | On      | Off  | On      |

| DS2    | Off     | In   | Off     |

| DS3    | Off     | Off  | Off     |

| DS4    | Off     | Off  | Off     |

| RN1    | Out     | In   | In      |

| S      | X       | X    | X       |

| R      | In      | In   | In      |

| I      | In      | In   | In      |

| C      | In      | In   | In      |

| D      | Out     | Out  | Out     |

| DC     | Out     | Out  | Out     |

| 25     | In      | In   | Tn      |

| SI     | Out     | Out  | Out     |

| S2     | In      | In   | In      |

| S3     | Out     | Out  | Out     |

| DL     | In      | Tn   | In      |

| DD     | In      | In   | In      |

| X      | Out     | Out  | Out     |

| A      | In      | In   | In      |

| В      | In      | In   | In      |

| RI     | In      | In   | Tn      |

| RR     | In      | In   | In      |

| NP     | Out     | Out  | Out     |

| WP     | In      | In   | In      |

| IU     | Out     | Out  | Out     |

| Y      | In      | In   | In      |

| Z      | Out     | Out  | Out     |

| но     | In      | In   | In      |

| DR     | Out     | Out  | Out     |

| E      | X       | X    | · X     |

| SS     | In      | In   | In      |

| HS     | Out     | Out  | Out     |

| NS     | In      | In   | In      |

| os     | Out     | Out  | Out     |

| FS     | Out     | Out  | Out     |

| TS     | In.     | In   | In      |

<sup>\*</sup> Terminators should be placed 'IN' on the drive which is physically the last one on the cable.

Table 2.4-C: Drive Configuration CDC P/N 9406-2/3 Drives Configured for RX03 Compatibility The QumeTrak 242 can be modified by the user. These changes are made by adding or deleting traces and by using the Alternate I/O pins. The following table shows the configuration of the option traces and jumpers as shipped from the factory.

|                         | Gruse Trae                       | From Fac | tory  |

|-------------------------|----------------------------------|----------|-------|

| Designator              | Description                      | Open     | Short |

| oesigne ee              |                                  | DS2,DS3  | DS1   |

| DS1-DS4                 | Drive Select Address Pins        | DS4      | 1002  |

|                         | (Up to 4 Drives)                 | X        |       |

| X                       | Radial Head Load                 |          |       |

| Z                       | In Use From Drive Select         | X        | X     |

| HL                      | Stepper Power From Head Load     |          | X     |

| R                       | Alternate Output Ready Pad       |          | X     |

| I                       | Alternate Output Index Pad       |          | X     |

| C                       | Alternate Input Head Load        |          | A     |

| D                       | Alternate Input In Use           | X        | _     |

| DC                      | Alternate Output Disk Change     | (X)      | 7     |

| 25                      | Alternate Output Two Sided Disk  |          | X     |

| Y                       | In Use From Head Load            |          | X     |

| DL                      | Door Lock Latch                  | X        | 14.44 |

| RR                      | Radial Ready                     |          | X     |

| RI                      | Radial Index                     |          | X     |

| WP                      | Inhibit Write When Write Protect |          | X     |

| NP                      | Allow Write When Write Protect   | X        |       |

| D1,D2,D4,               | Drive Address Select             | X        |       |

| DDS                     | (Up to 8 Drives)                 |          |       |

| B1-B4                   | Two, Double-Sided Drive Select   | X        |       |

| S1-S3                   | Head Select Option               | \$1,83   | S2    |

| T40                     | Test Track 40                    | X        |       |

| HA                      | Test Actuate Head Load           | X        |       |

| CONTROL CONTROL CONTROL | Alternate I/O Pins               | X        |       |

| 4,6,8,10                |                                  |          |       |

| 12,16,18,24             | Switch Filter                    |          | X     |

| SF                      | Stepper Power (Used With HL)     | X        |       |

| SP<br>A,B               | Radial Head Load                 | 4        | X     |

Table 2.4-D; Strappable Options

QumeTrak 242 Drive

#### 2.3 Cabling

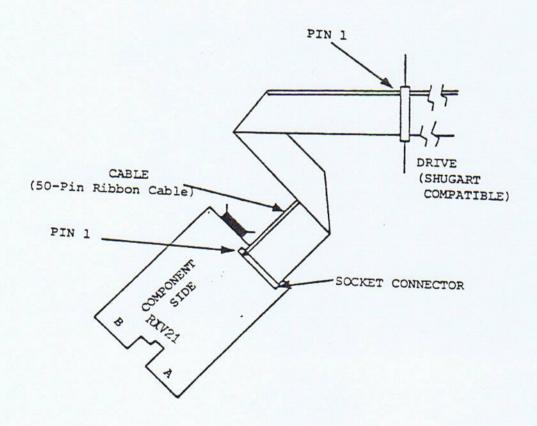

A 50 conductor ribbon cable connects the controller to any Shugart compatible drive(s). If the optional cable is purchased with the controller, connect the socket connector to the 50 pin header located at the edge of the controller board. Observe the alignment of pin 1 of the socket connector and header as indicated by the arrows shown in Figure 2.2. The two 50 pin connectors should be connected to the coresponding drives, again observing the location of pin 1. If the optional cable is purchased from an independent source, the following list of materials (or equivalent) will help in the construction of the required cable.

| QTY | DESCRIPTION               | MFG | P/N       |

|-----|---------------------------|-----|-----------|

| 1   | 50 pin socket connector   | 3M  | 3425-3000 |

| 2   | 50 pin edge connector     | 3M  | 3415-0001 |

| A/R | 50 conductor ribbon cable | 3M  | 3365/50   |

Figure 2.2 Drive/Controller Cabling

The connector pins illustrated in Figure 2.3 are compatible with both the Shugart 800 series and 850 series drives. Any drive that has both a Shugart compatible interface and connector should function properly with the controller.

| 1  | 2    | > /TG 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3  | 4    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5  | 6    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7  | 8    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9  | 10   | < /TWO SIDED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11 | 12   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13 | 14   | > /SIDE SELECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 15 | 16   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17 | 18   | > /HEAD LOAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 19 | 20   | < /INDEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 21 | 22   | < /READY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 23 | 24   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 25 | 26   | > /DRIVE SELECT 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 27 | 28   | > /DRIVE SELECT 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 29 | 30   | T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 31 | 32   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 33 | 34   | T> /DIRECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

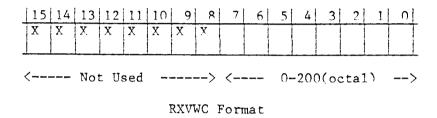

| 35 | 36   | > /STEP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |